Jacques Weber Sébastien Moutault Maurice Meaudre

# Le Langage VHDL

du langage au circuit, du circuit au langage

5e édition

#### Copyright couverture: © Fotolia

DANGER

Le pictogramme qui figure ci-contre mérite une explication. Son objet est d'alerter le lecteur sur la menace que

représente pour l'avenir de l'écrit, particulièrement dans le domaine de l'édition technique et universitaire, le développement massif du photocopillage.

Le Code de la propriété intellectuelle du 1<sup>er</sup> juillet 1992 interdit en effet expressément la photocopie à usage collectif sans autori-

sation des ayants droit. Or, cette pratique s'est généralisée dans les établissements d'enseignement supérieur, provoquant une baisse brutale des achats de livres et de revues, au point que la possibilité même pour

les auteurs de créer des œuvres nouvelles et de les faire éditer correctement est aujourd'hui menacée. Nous rappelons donc que toute reproduction, partielle ou totale, de la présente publication est interdite sans autorisation de l'auteur, de son éditeur ou du Centre français d'exploitation du

droit de copie (CFC, 20, rue des Grands-Augustins, 75006 Paris).

Le Code de la propriété intellectuelle n'autorisant, aux termes de l'article L. 122-5, 2° et 3° a), d'une part, que les «copies ou reproductions strictement réservées à l'usage privé du copiste et non destinées à une utilisation collective » et, d'autre part, que les analyses et les courtes citations dans un but d'exemple et d'illustration, « toute représentation ou reproduction intégrale ou partielle faite sans le consentement de l'auteur ou de ses ayants droit ou ayants cause est illicite » (art. L. 122-4).

Cette représentation ou reproduction, par quelque procédé que ce soit, constituerait donc une contrefaçon sanctionnée par les articles L. 335-2 et suivants du Code de la propriété intellectuelle.

# **Table des matières**

Partie A

ΧI

AVANT-PROPOS À LA CINQUIÈME ÉDITION

|               |                  | MODÉLISATION ET SYNTHÈSE : LE MÊME LANGAGE            |    |

|---------------|------------------|-------------------------------------------------------|----|

| 1             | Le lang          | age VHDL dans le flot de conception                   | 2  |

| 2             | Quels q          | ue soient l'outil et le circuit : la portabilité      | 6  |

| 3             | Deux vi          | sions complémentaires : hiérarchique et fonctionnelle | 7  |

|               |                  | Partie B                                              |    |

|               |                  | CONCEPTION ET TEST DES CIRCUITS NUMÉRIQUES            |    |

| <b>C</b> HAPI | TRE <b>1</b> • 1 | DÉCRIRE LE CIRCUIT                                    | 13 |

| 1.1           | La boîte         | e noire et son contenu                                | 13 |

|               | 1.1.1            | La boîte noire : une entité                           | 14 |

|               |                  | a) Déclaration d'entité                               | 14 |

|               |                  | b) Déclaration de port et modes d'accès               | 15 |

|               | 1.1.2            | Son contenu : une architecture                        | 17 |

|               |                  | a) Définition d'architecture                          | 17 |

|               |                  | b) Une description comportementale                    | 19 |

|               |                  | c) Une description flot de données                    | 21 |

|               |                  | d) Une description structurelle                       | 22 |

IV Le langage VHDL

| 1.2          | Décrire des opérateurs combinatoires |                                                                      |          |  |  |  |

|--------------|--------------------------------------|----------------------------------------------------------------------|----------|--|--|--|

|              | 1.2.1                                | Description par des instructions concurrentes                        | 24       |  |  |  |

|              |                                      | a) Équations logiques traditionnelles                                | 24       |  |  |  |

|              |                                      | b) Affectations structurées                                          | 25       |  |  |  |

|              | 1.2.2                                | Description par un algorithme séquentiel                             | 27       |  |  |  |

| 1.3          | Décrire                              | e des opérateurs séquentiels                                         | 30       |  |  |  |

|              | 1.3.1                                | Synchrone ou asynchrone?                                             | 31       |  |  |  |

|              | 1.3.2                                | Un opérateur asynchrone                                              | 32       |  |  |  |

|              | 1.3.3                                | Un opérateur synchrone                                               | 32       |  |  |  |

|              | 1.3.4                                |                                                                      |          |  |  |  |

|              | 1.3.5                                | Réinitialisation synchrone ou asynchrone?                            | 37       |  |  |  |

|              | 1.3.6                                | Un compteur – Le paquetage IEEE.NUMERIC_STD                          | 37       |  |  |  |

| 1.4          | Décrire                              | e des machines d'états synchrones                                    | 39       |  |  |  |

|              | 1.4.1                                | Une machine de Mealy                                                 | 42       |  |  |  |

|              | 1.4.2                                | Une machine de Moore                                                 | 45       |  |  |  |

|              | 1.4.3                                | Une machine de Medvedev                                              | 48       |  |  |  |

|              | 1.4.4                                | Moore, Medvedev, ou Mealy?                                           | 51       |  |  |  |

| 1.5          | Décrire                              | e des architectures et organiser le projet                           | 53       |  |  |  |

|              | 1.5.1                                | Factoriser le code                                                   | 54       |  |  |  |

|              |                                      | a) Sous-programmes : fonctions et procédures                         | 54       |  |  |  |

|              |                                      | b) Boucles dans l'univers séquentiel et dans l'univers concurrent    | 56       |  |  |  |

|              |                                      | c) Décrire des modules génériques                                    | 57       |  |  |  |

|              | 1.5.2                                | Construire l'architecture                                            | 61       |  |  |  |

|              |                                      | a) Par instanciation d'entité                                        | 62       |  |  |  |

|              |                                      | b) Par instanciation de composants                                   | 63       |  |  |  |

|              |                                      | c) À l'aide d'une configuration de composant                         | 64       |  |  |  |

|              | 1.5.3                                | Organiser le projet                                                  | 65       |  |  |  |

|              |                                      | a) Rassembler des composants dans un paquetage                       | 66       |  |  |  |

|              |                                      | b) Configurer un projet                                              | 67       |  |  |  |

|              |                                      | c) Constituer une bibliothèque                                       | 70       |  |  |  |

| <b>C</b> HAP | ITRE <b>2</b> •                      | TESTER SON FONCTIONNEMENT                                            | 71       |  |  |  |

| 2.1          | Structi                              | ure générale d'un banc de test                                       | 72       |  |  |  |

| 2.2          |                                      | Effectuer des tests unitaires                                        |          |  |  |  |

|              | 2.2.1                                | Des outils pour le test – Tester un module combinatoire              | 73<br>74 |  |  |  |

|              | 2.2.1                                | a) Générer des stimuli par des ondes projetées                       | 74       |  |  |  |

|              |                                      | b) Utiliser un fichier texte pour décrire le vecteur de test         | 75       |  |  |  |

|              |                                      | c) Générer des stimuli aléatoires                                    | 77       |  |  |  |

|              |                                      | d) Automatiser la vérification par des assertions                    | 78       |  |  |  |

|              |                                      | e) Sélectionner l'architecture du module testé par une configuration | 80       |  |  |  |

|              | 2.2.2 Tester un module séquentiel    |                                                                      |          |  |  |  |

|              |                                      | a) Un unique signal à l'origine de tout événement : l'horloge        | 81       |  |  |  |

|              |                                      | b) Générer des stimuli synchrones                                    | 83       |  |  |  |

Table des matières

|              | <ul> <li>c) Reproduire les réactions de l'environnement : le code bouchon</li> <li>d) Élaborer des espions de signaux</li> </ul> | 84<br>85 |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------|----------|--|

| 2.3          | Effectuer une vérification post-synthèse                                                                                         | 86       |  |

|              | ,                                                                                                                                |          |  |

| <b>C</b> HAP | ITRE <b>3 • QUELQUES PIÈGES</b>                                                                                                  | 91       |  |

| 3.1          | Les mémoires cachées                                                                                                             | 92       |  |

|              | 3.1.1 Un décodeur à maintien asynchrone                                                                                          | 92       |  |

|              | 3.1.2 Les indices de l'anomalie                                                                                                  | 93       |  |

|              | 3.1.3 Le remède                                                                                                                  | 94       |  |

| 3.2          | Signaux et variables                                                                                                             | 96       |  |

|              | 3.2.1 Un générateur de parité fantaisiste                                                                                        | 96       |  |

|              | 3.2.2 Variables et <i>latch</i> 3.2.3 Variables et bascules                                                                      | 97<br>98 |  |

| 3.3          | Automates : codage des états                                                                                                     | 100      |  |

| 3.4          | Les boucles                                                                                                                      | 102      |  |

| 3.4          | 3.4.1 Des boucles non synthétisables                                                                                             | 102      |  |

|              | 3.4.2 Des boucles inutiles                                                                                                       | 103      |  |

| 3.5          | La complexité sous-jacente                                                                                                       | 104      |  |

| 3.6          | De l'ordre dans les horloges                                                                                                     |          |  |

|              | 3.6.1 Des horloges mélangées aux commandes                                                                                       | 106      |  |

|              | 3.6.2 Les horloges multiples                                                                                                     | 107      |  |

| 3.7          | Conflits et signaux trois états                                                                                                  |          |  |

|              | 3.7.1 Des opérateurs trois états qui n'en sont pas                                                                               | 108      |  |

|              | 3.7.2 Des pilotes multiples                                                                                                      | 109      |  |

| 3.8          | Penser « circuit »                                                                                                               | 110      |  |

|              | <b>P</b> artie <b>C</b>                                                                                                          |          |  |

|              | - FARTIE C                                                                                                                       |          |  |

|              | SIMULATION, DE LA SÉMANTIQUE DU LANGAGE VHDL<br>AU MODÈLE RÉTRO-ANNOTÉ VITAL                                                     |          |  |

| CHAD         | ITRE <b>4 • PARALLÉLISME ET ALGORITHMES SÉQUENTIELS</b> :                                                                        |          |  |

|              | UX, VARIABLES ET PROCESSUS                                                                                                       | 113      |  |

| 4.1          | Parallélisme                                                                                                                     | 114      |  |

|              | 4.1.1 Les processus : des algorithmes simultanés en boucles infinies                                                             | 114      |  |

|              | 4.1.2 Causalité et parallélisme : les pilotes de signaux                                                                         | 116      |  |

|              | a) Gestion des événements                                                                                                        | 117      |  |

|              | b) Convergence                                                                                                                   | 119      |  |

VI Le langage VHDL

|              | 4.1.3                                                           | Conflits                                                     | 120        |  |  |

|--------------|-----------------------------------------------------------------|--------------------------------------------------------------|------------|--|--|

|              |                                                                 | a) Fonction de résolution                                    | 121        |  |  |

|              |                                                                 | b) Sorties non standard (trois états et collecteurs ouverts) | 123        |  |  |

| 4.2          | Signaux et variables                                            |                                                              |            |  |  |

| 4.3          | Durée de vie des variables : procédures, fonctions et processus |                                                              |            |  |  |

| 4.4          | Gestio                                                          | Gestion du temps simulateur                                  |            |  |  |

|              | 4.4.1                                                           | Introduire des retards                                       | 130        |  |  |

|              | 4.4.2                                                           | Modes de diffusion                                           | 132        |  |  |

|              |                                                                 | a) Mode inertiel et mode transport                           | 132        |  |  |

|              |                                                                 | b) Réjection des impulsions parasites                        | 133        |  |  |

|              | 4.4.3                                                           | Fonction NOW                                                 | 133        |  |  |

|              | 4.4.4                                                           | Attributs attachés à un signal                               | 134        |  |  |

| CUAD         | ITDE <b>5</b> .                                                 | BUS, CONFLITS ET ARITHMÉTIQUE DE VECTEURS :                  |            |  |  |

|              |                                                                 | EEE-1076.3                                                   | 135        |  |  |

| 5.1          | l es pa                                                         | quetages du standard IEEE-1076.3                             | 136        |  |  |

| 5.2          | Des types logiques simples multivalués                          |                                                              |            |  |  |

| ٦.٢          |                                                                 |                                                              | 138<br>139 |  |  |

|              | 5.2.1                                                           | Les types STD_ULOGIC et STD_LOGIC  Nombres et vecteurs       | 139        |  |  |

| F 2          |                                                                 |                                                              |            |  |  |

| 5.3          | Des opérateurs prédéfinis                                       |                                                              |            |  |  |

|              |                                                                 | Les opérateurs arithmétiques                                 | 142        |  |  |

|              | 5.3.2                                                           | Les opérateurs relationnels                                  | 142        |  |  |

| <b>C</b> HAP | ITRE 6 •                                                        | COMMUNIQUER AVEC L'ENVIRONNEMENT ET LE SIMULATEUR            | 145        |  |  |

| 6.1          | Fichier                                                         | s (STD.TEXTIO)                                               | 145        |  |  |

|              | 6.1.1                                                           | Déclaration et ouverture                                     | 145        |  |  |

|              | 6.1.2                                                           | Le paquetage STD.TEXTIO                                      | 147        |  |  |

|              | 6.1.3                                                           | Le paquetage IEEE.STD_LOGIC_TEXTIO                           | 151        |  |  |

|              | 6.1.4                                                           | Les entrées sorties standard                                 | 153        |  |  |

| 6.2          | Instruc                                                         | tions ASSERT et REPORT                                       | 154        |  |  |

|              | 6.2.1                                                           | Tester une condition : ASSERT                                | 154        |  |  |

|              | 6.2.2                                                           | Signaler un événement : REPORT                               | 155        |  |  |

|              | 6.2.3                                                           | Identifier un objet grâce aux attributs                      | 155        |  |  |

| CHAR         | ITDE <b>7</b> .                                                 | VIOLATION DES RÈGLES TEMPORELLES : DES MODÈLES « MAISON »    |            |  |  |

|              | IBRAIRIE                                                        |                                                              | 157        |  |  |

| 7.1          | Des modèles « maison »                                          |                                                              |            |  |  |

|              | 7.1.1                                                           | Un modèle naïf                                               | 158        |  |  |

|              | 7.1.2                                                           | La construction d'une bibliothèque                           | 159        |  |  |

|              |                                                                 | L'utilisation de la bibliothèque                             | 161        |  |  |

163

166

|               |                  | Partie D                                                                                             |                                               |

|---------------|------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|               |                  | LE LANGAGE VHDL, ÉLÉMENTS DE SYNTAXE                                                                 |                                               |

| Снарі         | TRE <b>8</b> •   | UN PRÉLIMINAIRE GRAMMATICAL : LE FORMALISME DE BACKUS ET NAUR (BNF)                                  | 171                                           |

| <b>C</b> HAPI | TRE <b>9</b> . L | LES OBJETS DU LANGAGE                                                                                | 175                                           |

| 9.1           | Les mo           | ts réservés                                                                                          | 175                                           |

| 9.2           | Une str          | ructure de blocs homogène                                                                            | 176                                           |

| 9.3           | 9.3.1            | de conception : entité et architecture<br>La déclaration d'entité<br>L'architecture                  | 177<br>177<br>178                             |

| 9.4           | Types 6          | et classes                                                                                           | 180                                           |

|               | 9.4.1            | Les types scalaires  a) Types énumérés  b) Types entiers  c) Types physiques  d) Types flottants     | 181<br>181<br>182<br>182<br>183               |

|               | 9.4.2            | Les types structurés  a) Tableaux  b) Enregistrements                                                | 183<br>183<br>184                             |

|               | 9.4.3            | Fichiers et pointeurs  a) Fichiers  b) Pointeurs                                                     | 185<br>185<br>185                             |

|               | 9.4.4            | Constantes signaux et variables  a) Constantes  b) Signaux  c) Variables                             | 186<br>186<br>187<br>188                      |

|               | 9.4.5            | Alias                                                                                                | 189                                           |

| 9.5           | 9.5.1<br>9.5.2   | Opérateurs Opérandes a) Les noms b) Les constantes littérales c) Les agrégats d) Précisions de types | 189<br>189<br>192<br>192<br>194<br>195<br>196 |

| 9.6           | Attribu          | uts                                                                                                  | 196                                           |

|               | 9.6.1<br>9.6.2   | Attributs prédéfinis<br>Attributs définis par l'utilisateur                                          | 197<br>200                                    |

7.2

7.3

Les primitives VITAL

Les fichiers de timings

VIII Le langage VHDL

| <b>C</b> HAPI | TRE <b>10</b> •                | LES INSTRUCTIONS                                          | 201 |

|---------------|--------------------------------|-----------------------------------------------------------|-----|

| 10.1          | Instructions concurrentes      |                                                           |     |

|               | 10.1.1 Affectations de signaux |                                                           |     |

|               | 10.1.2 I                       | Instanciation de composants, d'entité ou de configuration | 203 |

|               | 10.1.3 N                       | Modules de programme                                      | 204 |

|               | C                              | a) Bloc                                                   | 205 |

|               | ŀ                              | b) Processus                                              | 206 |

|               | 10.1.4                         | Algorithmes spatiaux (GENERATE)                           | 207 |

|               | C                              | a) Boucles et tests dans l'univers concurrent             | 207 |

|               | ŀ                              | b) Instanciations multiples : des schémas algorithmiques  | 208 |

| 10.2          | Instructio                     | ons séquentielles                                         | 208 |

|               | 10.2.1 I                       | L'instruction WAIT                                        | 208 |

|               | 10.2.2 I                       | La liste de sensibilité                                   | 209 |

|               | 10.2.3 I                       | Réaction immédiate : affectation de variable              | 210 |

|               | 10.2.4 I                       | Réaction différée : affectation séquentielle de signal    | 210 |

|               | 10.2.5                         | Test et sélection                                         | 210 |

|               | C                              | a) Tests logiques                                         | 211 |

|               | l                              | b) Sélections                                             | 211 |

|               | 10.2.6 I                       | Boucles                                                   | 212 |

| <b>C</b> HAPI | TRE <b>11</b> •                | STRUCTURES D'UN PROGRAMME                                 | 215 |

| 11.1          | Les sous-                      | programmes : procédures et fonctions                      | 215 |

|               | 11.1.1 5                       | Syntaxe                                                   | 216 |

|               | 11.1.2 \$                      | Surcharges de sous-programmes                             | 219 |

|               | C                              | a) Des actions adaptées aux types des arguments           | 219 |

|               | l                              | b) Surcharge d'opérateurs                                 | 220 |

| 11.2          | Librairies                     | et paquetages                                             | 220 |

|               | 11.2.1 I                       | Fichiers sources et unités de conception                  | 221 |

|               | C                              | a) Spécifications de contexte                             | 221 |

|               | ŀ                              | b) Paquetages                                             | 222 |

|               | 11.2.2 I                       | La librairie WORK                                         | 222 |

|               | 11.2.3 I                       | La librairie STD                                          | 223 |

|               | C                              | a) Le paquetage STD.STANDARD                              | 223 |

|               | ŀ                              | b) Le paquetage STD.TEXTIO                                | 223 |

| 11.3          | Construct                      | tion hiérarchique                                         | 224 |

|               | 11.3.1 I                       | Blocs externes et blocs internes                          | 224 |

|               | 11.3.2                         | Configuration d'un projet                                 | 225 |

|               | C                              | a) Spécification de la configuration d'un composant       | 225 |

|               | l                              | b) Déclaration de configuration d'une entité              | 226 |

# Partie E

IX

## UN LANGAGE EN ÉVOLUTION

| <b>C</b> HAPI | TRE <b>12 • VHDL-2008</b>                               | 231 |  |

|---------------|---------------------------------------------------------|-----|--|

| 12.1          | Décrire structures et opérations sans fixer les détails | 233 |  |

|               | 12.1.1 Au-delà des génériques comme simples paramètres  | 233 |  |

|               | a) Les types génériques                                 | 233 |  |

|               | b) Liste de génériques dans un sous-programme           | 234 |  |

|               | c) Liste de génériques dans un paquetage                | 235 |  |

|               | d) Sous-programme générique                             | 236 |  |

|               | 1.2 Des types structurés non-contraints                 | 237 |  |

| 12.2          | Une librairie IEEE enrichie                             | 237 |  |

|               | 12.2.1 Les paquetages « historiques »                   | 238 |  |

|               | a) Le paquetage std_logic_1164                          | 238 |  |

|               | b) Les paquetages numeric_std et numeric_bit            | 238 |  |

|               | 12.2.2 Les nombres en virgule fixe                      | 238 |  |

|               | 12.2.3 Les nombres en virgule flottante                 | 240 |  |

|               | 12.2.4 Des précautions en synthèse                      | 241 |  |

| 12.3          | Une syntaxe simplifiée et enrichie                      |     |  |

|               | 12.3.1 Facilité d'accès aux ports d'une entité          | 243 |  |

|               | 12.3.2 Liste de sensibilité implicite                   | 244 |  |

|               | 12.3.3 Affectations conditionnelles et sélectives       | 244 |  |

|               | 12.3.4 Instructions case et select hiérarchiques        | 244 |  |

|               | 12.3.5 Instruction generate                             | 245 |  |

|               | 12.3.6 Opérateurs logiques                              | 246 |  |

|               | a) Opérateurs logiques de réduction                     | 246 |  |

|               | b) Opérateurs entre scalaires et tableaux               | 246 |  |

|               | c) Opérateur de condition                               | 246 |  |

|               | d) Opérateurs relationnels                              | 247 |  |

|               | 12.3.7 Minimum et maximum                               | 248 |  |

| 12.4          |                                                         | 248 |  |

|               | 12.4.1 Accéder aux nœuds internes d'un circuit          | 248 |  |

|               | 12.4.2 Forcer une valeur                                | 249 |  |

|               | 12.4.3 Assertions, propriétés et séquences              | 249 |  |

| 12.5          | Un pas vers la programmation objet : les types protégés | 250 |  |

| 12.6          | Divers                                                  | 251 |  |

|               | 12.6.1 La spécification de contexte                     | 251 |  |

|               | 12.6.2 Des entrées sorties améliorées                   | 252 |  |

|               | 12.6.3 Crypter les sources                              | 253 |  |

X Le langage VHDL

| C       | 42                                                       |     |

|---------|----------------------------------------------------------|-----|

| CHAPI   | TRE <b>13 •</b> LA BIBLIOTHEQUE OSVVM                    | 255 |

| 13.1    | Architecture d'un banc de vérification                   | 256 |

| 13.2    | Randomisation sous contrainte                            | 258 |

|         | 13.2.1 Principe                                          | 258 |

|         | 13.2.2 Les types de données randomisables                | 259 |

|         | 13.3.3 Imposer la loi de distribution et les contraintes | 260 |

| 13.3    | Couverture                                               | 261 |

|         | 13.3.1 Principe                                          | 261 |

|         | 13.3.2 Valeurs comptées, ignorées, interdites            | 263 |

|         | 13.3.3 Croiser les données                               | 264 |

| 13.4    | Piloter la vérification par la couverture                | 265 |

| EXERCIO | CES                                                      | 267 |

| BIBLIOG | GRAPHIE                                                  | 285 |

| INDEX   |                                                          | 287 |

# Avant-propos à la cinquieme édition

Le langage VHDL évolue pour prendre aujourd'hui en charge l'activité de vérification. L'apparition de la norme 2008 a marqué une première étape importante vers cet objectif. La seconde étape, la création de bibliothèques spécialisées dans la vérification, était déjà annoncée. En 2012, l'apparition de la bibliothèque OSVVM (*Open Source VHDL Verification Methodology*) a marqué le point de départ de cette seconde étape.

La principale nouveauté de cette cinquième édition est la présentation des principales fonctionnalités offertes par cette toute récente bibliothèque de vérification.

Les outils de simulation, et a fortiori de synthèse, acceptent encore aujourd'hui diversement VHDL-2008, nous avons donc conservé dans le corps de l'ouvrage le standard, universellement reconnu, de la norme VHDL-1993. La dernière partie de l'ouvrage se consacre aux nouveautés liées au standard 2008.

Cette cinquième édition est articulée en cinq parties qui correspondent à des approches complémentaires :

- Une introduction générale présente l'ensemble du sujet : la réalisation (synthèse) et le test des circuits numériques, en utilisant VHDL. La description du circuit à réaliser et la simulation tant au niveau fonctionnel que post-synthèse se fait en utilisant ce même langage évolué. Cette unicité dans les différents niveaux de description est l'une des raisons de la généralisation des langages évolués dans le domaine de la conception de circuits.

- La seconde partie permet au lecteur de découvrir l'ensemble des possibilités offertes par le langage pour la synthèse et le test des circuits numériques, en suivant une démarche qui conduit à une application facile à implanter dans un circuit programmable (FPGA). Moyennant l'emploi de cartes d'évaluation et d'outils de développement (Altera ou Xilinx) très répandus dans les établissements

d'enseignement et les entreprises, le lecteur peut immédiatement mettre en œuvre les exemples supports. La même partie présente un panorama des pièges les plus classiques rencontrés dans cette démarche d'élaboration d'un nouveau composant numérique.

- La troisième partie apporte des compléments d'information sur la sémantique du langage et sur les outils de modélisation. À partir d'exemples très simples, le lecteur y découvre les principes de la modélisation des limites de fonctionnement des circuits numériques. Cette partie est complétée par la présentation d'un ensemble d'outils standardisés de simulation post-synthèse, utilisés par tous les grands fabricants de circuits programmables et d'ASIC : la librairie VITAL.

- La quatrième partie est une récapitulation de la syntaxe du langage VHDL. Cette partie a vocation à servir de référence au programmeur qui y trouvera décrites la plupart des constructions utiles en conception de circuit, avec des exemples simples ou des renvois à des applications tirées de la seconde partie.

- La dernière partie est consacrée aux dernières évolutions de VHDL et son univers, c'est-à-dire le standard VHDL-2008 et la bibliothèque OSVVM.

Les exemples, pris comme colonne vertébrale de la seconde partie, ont été choisis suffisamment classiques pour que de nombreux lecteurs en connaissent les principes; ils illustrent la grande majorité des constructions utilisées en synthèse des systèmes numériques.

L'ordre de lecture n'est pas impérativement celui de l'organisation du livre : le lecteur qui souhaite privilégier un aperçu général du langage, avant d'explorer en détail les exemples de la seconde partie, peut très bien établir un parcours différent (parties A, D, C puis B, par exemple).

De nombreuses ressources Internet sont liées à cet ouvrage : les exemples du livre bien sûr, mais aussi des liens vers des fabricants de circuits, d'outils logiciels ou des sites dédiés à VHDL. On trouvera également sur le site un chapitre sur les circuits programmables, un aperçu sur le monde des « systèmes complexes sur une puce », sur celui des modules *IP* (*Intellectual Property*), sur celui du standard *WISHBONE* d'interconnexion de tels modules et des exercices sont également mis à disposition du lecteur. Toutes ces ressources sont accessibles sur le site de l'éditeur : www.dunod.com.

Jacques Weber Sébastien Moutault

À la mémoire de Maurice Meaudre, à qui ce livre doit beaucoup, décédé avant la publication de la troisième édition de ce livre.

### Partie A

# MODÉLISATION ET SYNTHÈSE : LE MÊME LANGAGE

Représentation spatiale et analyse séquentielle <sup>1</sup> : la première privilégie le global, l'organisation, les relations, dans un traitement parallèle (et/ou simultané); la seconde décompose, analyse les successions d'événements, décrit les causalités.

Les deux visions sont nécessaires à la description des circuits électroniques. Elles produisent, dans les approches traditionnelles, deux catégories de langages, complémentaires mais disjoints : les schémas et les algorithmes<sup>2</sup>. Tenter de saisir le fonctionnement d'un microprocesseur à partir de son schéma électrique est illusoire, l'expliquer par un algorithme également<sup>3</sup>.

Les langages de description du matériel, traduction littérale de *hardware description language* (HDL), se doivent de marier les deux approches. Le même langage permet, à tous les niveaux d'une représentation hiérarchique, d'associer les aspects structurels et les aspects fonctionnels, l'espace et le temps. VHDL est l'un de ces langages, il y en a d'autres, VERILOG, par exemple. Nous avons choisi, ici, d'explorer un peu le premier.

L'origine du langage suit une histoire un peu banale dans sa répétition<sup>4</sup> : le développement de l'informatique, la complexité croissante des circuits, ont fait fleurir une

<sup>1.</sup> Hémisphères droit et gauche du cerveau humain, diront certains. Mais c'est une autre histoire.

<sup>2.</sup> Peu importe, à ce niveau, le support physique utilisé, graphique ou textuel. Un schéma peut être décrit par un dessin, le monde graphique, ou par une *net list*, le monde textuel. De même, un algorithme peut être décrit par un diagramme (*flowchart*), le monde graphique, ou par un langage procédural, le monde textuel. Chaque représentation a ses avantages et ses inconvénients.

<sup>3.</sup> La deuxième tentative est, en outre, fausse. Elle ne prend pas en compte le parallélisme inhérent à tout système électronique.

<sup>4.</sup> Toute ressemblance avec ADA serait purement fortuite.

multitude de langages plus ou moins compatibles entre eux, plus ou moins cohérents entre synthèse (fabrication) et simulation (modélisation). Le programme VHSIC (*very high speed integrated circuits*), impulsé par le département de la défense des États-Unis dans les années 70-80, a donné naissance à un langage : VHSIC-HDL, ou VHDL.

Trois normes successives (IEEE¹-1076-1987, 1993 et 2008) en ont stabilisé la définition, complétées par des retouches et quelques extensions. La norme la plus majoritairement supportée par les outils reste aujourd'hui celle de 1993. Nous verrons les principales modifications apportées par la dernière mouture du langage (2008) à la fin de cet ouvrage. La prochaine évolution majeure consistera à intégrer les outils nécessaires à l'élaboration de bancs de vérification abstraits, outils déjà supportés par le principal concurrent de VHDL (voir *Le langage SystemVerilog* des mêmes auteurs).

« Apprendre à communiquer en une langue nouvelle prend toujours l'allure d'un défi. Au début, il semble que tout est nouveau, et doit être assimilé avant de caresser l'espoir d'utiliser le langage. Puis, après une première expérience, il apparaît des points de ressemblance avec notre propre langage. Au bout d'un moment, nous réalisons que les deux langages ont de nombreuses racines communes. »

Cette première phrase de *ADA une introduction*, par H. LEDGARD, résume on ne peut mieux la difficulté. Par où commencer?

Nous commencerons par les principes, les idées directrices, avant de nous jeter à l'eau dans la partie suivante.

#### 1 LE LANGAGE VHDL DANS LE FLOT DE CONCEPTION

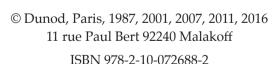

Les différentes étapes de la conception d'un circuit intégré sont illustrées par le diagramme de la figure A.1.

**Figure A.1** Étapes de conception d'un circuit.

<sup>1.</sup> Institute of Electrical and Electronics Engineers.

Dunod – La photocopie non autorisée est un délit.

L'ensemble du processus qui permet de passer de la vision fonctionnelle au circuit constitue la synthèse.

#### Un langage commun

Le principe majeur de VHDL est de fournir un langage commun, depuis la description au niveau système jusqu'au circuit. À tous les niveaux de description le langage est le même. Le découpage en étapes, illustré par la figure A.1, n'est pas toujours aussi schématique, il peut y en avoir plus comme il peut en manquer.

#### > Tout n'est pas synthétisable

Créer un langage, qui permette à la fois de valider une conception au niveau système, de construire les programmes de test utiles à tous les niveaux et de générer automatiquement des schémas d'implantation sur le silicium, est évidemment un propos ambitieux. VHDL est donc beaucoup plus qu'une simple traduction textuelle de la structure interne d'un circuit.

Les constructions légales ne sont pas toutes synthétisables, seul un sous-ensemble des instructions permises par le langage fait sens en synthèse. L'aboutissement – heureux cela va sans dire – d'un projet implique une vision précise de la différence entre la réalité du silicium et le monde virtuel qui sert à le concevoir. Comme tout langage de haut niveau, VHDL est modulaire. Cette modularité permet de voir un schéma complexe comme l'assemblage d'unités plus petites, elle contribue également à séparer le réel du virtuel.

Sans rentrer ici dans des exemples techniques – nous les aborderons plus avant – indiquons simplement qu'un modèle VHDL peut détecter des incohérences dans les signaux qui lui sont transmis, des fautes de *timing*, par exemple. Face à une telle situation le modèle peut interagir avec le simulateur, modifier les conditions du test, avertir l'utilisateur par des messages ou consigner des résultats dans un fichier. De tels modules de programme ne sont évidemment pas synthétisables. Parfois la distance entre synthèse et modélisation est plus ténue : générer un retard de 13 nano-secondes, par exemple, n'est pas, dans l'absolu impensable. Mais comment créer ce retard dans un circuit cadencé par une horloge à 100 MHz?

#### Simulation fonctionnelle

Tester un circuit revient à lui appliquer des stimuli, des vecteurs de test, et à analyser sa réponse. À un deuxième niveau, le test inclut l'environnement dans lequel le circuit est immergé, la carte sur laquelle il est implanté. Les conditions expérimentales reproduiront, dans un premier temps, les conditions de fonctionnement normales. Dans un deuxième temps elles chercheront à cerner les limites, une fréquence maximum, par exemple.

Tester un module logiciel revient à écrire un programme qui lui transmet des données, reçoit les résultats et les analyse. Dans une première étape les données transmises sont celles attendues, elles servent à identifier d'éventuelles erreurs

grossières. Dans une deuxième étape, les données sortent de l'ordinaire prévu, provoquent une situation de faute. Les exemples informatiques abondent, en voici un : quand on réalise un programme de tracé de courbes ou une calculatrice graphique, demander le tracé de  $y = x^2$  est un test de la première catégorie, celui de  $y = log [sin (1/x^2)]$  de la seconde <sup>1</sup>.

VHDL est un langage informatique qui décrit des circuits. Les programmes de test simulent l'environnement d'un montage, ils bénéficient de la souplesse de l'informatique pour recréer virtuellement toutes les situations expérimentales possibles et imaginables, même celles qui seraient difficiles à réaliser en pratique.

Le test est une opération psychologique difficile à mener : nous avons une fâcheuse tendance à vouloir nous convaincre nous-mêmes de la justesse de notre réalisation, à construire des tests qui nous conforteront dans cette idée. Or le but du test est de chercher la faute, même, et surtout, la faute maligne, celle qui ne se révèle pas au premier abord<sup>2</sup>.

#### > Du langage au circuit : la synthèse

Le synthétiseur interprète un programme et en déduit une structure de schéma. Dans une deuxième étape, il cherche à reproduire ce schéma dans une technologie, au moindre coût (surface de silicium), avec l'efficacité la plus grande (vitesse maximum).

Considérons un exemple simple : on souhaite réaliser la somme de deux nombres entiers, et stocker le résultat dans un registre synchrone, qui dispose d'une remise à zéro synchrone.

La partie active du code VHDL, traduisant ces opérations élémentaires, est indiquée ci-dessous :

```

-- ceci est un commentaire,

-- il va jusqu'à la fin de la ligne.

somme : PROCESS

BEGIN

WAIT UNTIL RISING_EDGE(hor); -- attente du front montant

IF raz = '1' THEN -- commande de remise à zéro

reg <= 0;

ELSE -- addition

reg <= e1 + e2;

END IF;

END PROCESS somme:

```

De ce programme le synthétiseur infère la présence d'un registre synchrone (des bascules D) pour stocker le résultat *reg*, grâce à l'instruction d'attente d'un front d'horloge. Il infère un bloc de calcul qui renvoie la somme des deux opérandes et l'affecte au contenu du registre.

<sup>1.</sup> Dans une première étape on peut supprimer le logarithme. L'intervalle de variation intéressant est évidemment centré autour de 0, comme {-1..1}.

<sup>2.</sup> Une situation de débordement dans un calcul numérique, par exemple.

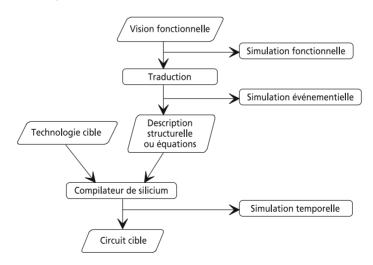

D'où la structure de la figure A.2.

Figure A.2 Un additionneur.

Dans cette architecture, de nombreux points restent à préciser : quels sont les types des opérandes et du résultat ? Quelles sont leurs tailles, en nombre de chiffres binaires ? Comment réaliser l'addition compte tenu du circuit cible ?

Les réponses aux premières de ces questions se trouvent dans des zones déclaratives :

```

PORT (hor, raz : IN STD_LOGIC; -- signaux binaires

e1, e2 : IN INTEGER RANGE 0 TO 15; -- entiers 4 bits

reg : OUT INTEGER RANGE 0 TO 31); -- entiers 5 bits

```

Le schéma comportera donc cinq bascules. À propos de ces premières instructions VHDL, nous découvrons l'importance des déclarations, l'omission de la restriction du domaine de variation des nombres conduirait, par défaut, à générer systématiquement un additionneur 32 bits.

La réponse à la dernière des questions précédentes ne se trouve pas dans le programme source. Elle fait partie intégrante de l'outil de synthèse, et dépend du circuit cible. Si ce dernier ne comporte comme opérateurs combinatoires élémentaires que des portes logiques, le synthétiseur devra être capable de traduire l'addition binaire en équations logiques, chiffre binaire par chiffre binaire. Si le circuit cible comporte des blocs arithmétiques, le synthétiseur tentera de les utiliser. Souvent la réalité se situe à mi-chemin entre logiciel et matériel : le circuit ne comporte que des opérateurs logiques, mais le compilateur de silicium possède des bibliothèques fournies de fonctions standard précompilées et optimisées. La traduction l' du code source revient alors à reconnaître lesquelles de ces fonctions peuvent être utiles.

Le programmeur attendrait, d'un outil de CAO idéal, que toutes les réponses non inscrites dans le programme source soient fournies automatiquement, au mieux de ses intérêts, sans qu'il ait à s'en préoccuper. Ne nous leurrons pas, une bonne connaissance des circuits utilisés reste nécessaire, quelle que soit la qualité des logiciels employés.

Dunod – La photocopie non autorisée est un délit.

<sup>1.</sup> Avec un certain humour, les auteurs d'un tel traducteur, qui s'adapte aux familles de circuits cibles, l'avaient baptisé *metamor* (utilisé il y a une dizaine d'années par SYNARIO, de DATA IO).

#### Du circuit au langage : la modélisation

La réalité du monde physique introduit des différences de comportement entre le modèle fonctionnel et sa réalisation dans un circuit. Les principales de ces différences proviennent des temps de calcul des opérateurs. Une fois le programme compilé, traduit en un schéma de portes et de bascules interconnectées, il est intéressant de prévoir, compte tenu de la technologie employée, les limites de son fonctionnement. Cette opération de modélisation post-synthèse est connue sous le terme de *rétro-annotation*.

Un modèle rétro-annoté réalise – c'est du moins souhaitable – la même fonction que le modèle synthétisable dont il est issu, mais il apporte des renseignements complémentaires concernant les limites de fonctionnement que l'on peut attendre du circuit. On peut remarquer que le modèle rétro-annoté n'est, lui, pas synthétisable! Il représente une réalité qu'il est incapable de créer <sup>1</sup>.

### 2 QUELS QUE SOIENT L'OUTIL ET LE CIRCUIT : LA PORTABILITÉ

La *portabilité* <sup>2</sup> est le maître mot. Dans le monde des circuits ce mot a un double sens : portabilité vis-à-vis des circuits et portabilité vis-à-vis des logiciels de conception.

#### Indépendance vis-à-vis du circuit cible

Le même langage peut servir à programmer un circuit de quelques centaines de portes équivalentes, et à concevoir un circuit intégré spécifique qui en contient plusieurs millions. Les compilateurs utilisés n'ont, bien sûr, pas grand-chose en commun; le nombre de personnes impliquées dans un projet non plus. Mais le langage est le même<sup>3</sup>. Cette indépendance vis-à-vis du circuit cible a des applications industrielles : elle permet, par exemple, de commencer une réalisation avec des circuits programmables, dont le cycle de réalisation est simple et rapide, pour passer à un circuit spécifique dans une deuxième étape. La première version sert de prototype à la seconde.

<sup>1.</sup> Le rêve de tout électronicien : diminuer les temps de retard du modèle rétro-annoté pour augmenter la fréquence de travail du circuit réel.

<sup>2.</sup> Nous pouvons compléter, à la lumière de ce paragraphe, une remarque précédente que nous avions faite à propos des représentations graphique et textuelle. La représentation graphique a des aspects séduisants de lisibilité, c'est évident. Elle pose cependant un problème non trivial de portabilité (rares sont les outils graphiques universels) et de rigueur. Une représentation textuelle est moins intuitive, mais ne pose pas de problème de portabilité et permet une formalisation plus aisée, qui lui assure un caractère non ambigu. De nombreux systèmes proposent les deux modes; le mode graphique reste local, le passage d'un système à un autre se fait par l'intermédiaire du langage textuel.

<sup>3.</sup> Un langage n'est qu'un outil. Mais les langages de haut niveau ne sont pas neutres au niveau des méthodes de travail qu'ils induisent. Dans un contexte d'apprentissage, il est intéressant de disposer d'outils de développement petits et bon marché, qui permettent de développer des applications suffisamment simples pour être menées à terme par une seule personne en quelques heures.

#### ➤ Indépendance vis-à-vis du compilateur

Le deuxième aspect de la portabilité concerne les outils de développement. Le même programme est accepté par des logiciels de CAO très divers.

Historiquement, cette portabilité était excellente en simulation, c'est la moindre des choses, mais présentait des limitations sévères en synthèse. Pour un synthétiseur, certaines constructions sont un peu « magiques » : elles orientent le compilateur vers des opérations spécifiques, grâce à un sens caché qu'il est le seul à connaître. Ces particularismes locaux sont souvent liés à des définitions de types de données <sup>1</sup>, qui figurent dans des librairies spécifiques d'un outil. La règle en VHDL est de fournir les codes sources des librairies, règle respectée par tous les fournisseurs; mais cette (bonne) habitude, si elle assure une portabilité sans faille des outils de synthèse aux outils de simulation, ne peut évidemment pas assurer le portage des aspects magiques cachés. L'exemple caractéristique de données à caractère caché est la modélisation des bus. Le langage n'avait pas, volonté d'ouverture ou omission, prévu les logiques trois états dans ses types de base. En simulation, rien n'est plus simple que de construire de nouveaux types : tout est prévu. En synthèse, l'apparition d'un signal qui peut prendre deux états logiques et un état haute impédance, provoque la génération d'opérateurs très particuliers, qui échappent au monde des équations booléennes. Il y a un sens caché attaché à un type trois états. Tous les fournisseurs de logiciel ont défini leurs propres librairies synthétisables, toutes sensiblement équivalentes... mais strictement incompatibles.

Un effort de standardisation a été entrepris, entre 1993 et 1995, pour assurer une portabilité des programmes tant en synthèse qu'en simulation. Entre 1995 et 1997, tous les outils de conception de circuits programmables, par exemple, ont rejoint les nouveaux standards (IEEE-1076.3).

Le même type d'évolution a eu lieu dans le domaine de la rétro-annotation. Des modèles maison portables, puisque fournis sous forme de sources, au prix d'échanges de librairies volumineuses, on est passé, avec le standard IEEE-1076.4 (ou VITAL-95), à une compatibilité entre les bibliothèques des différents fondeurs. Cette compatibilité assure, de plus, une passerelle avec le monde VERILOG, riche en compétences et en expérience dans ce domaine.

# 3 DEUX VISIONS COMPLÉMENTAIRES : HIÉRARCHIQUE ET FONCTIONNELLE

Représentation spatiale et analyse séquentielle: VHDL favorise une approche hiérarchique pour la description d'un circuit complexe. Du niveau le plus élémentaire (les portes) au niveau le plus élevé (le système) le programmeur peut, définir à sa guise des sous-ensembles en relations, décrire un sous-ensemble par une représentation

<sup>1.</sup> Les seuls types que nous avons rencontrés, pour l'instant, sont les types entier et bit; il y en a d'autres.

comportementale (analytique) ou par une nouvelle hiérarchie locale. Les deux approches peuvent coexister dans un même programme source, et l'utilisateur peut spécifier à tout moment quelle configuration il choisit d'analyser.

#### > Construction hiérarchique

Reprenons l'exemple de notre additionneur. Un lecteur pointilleux pourra nous objecter que nous en avons fait une représentation graphique structurelle, et que nous l'avons décrit par un programme comportemental. C'est on ne peut plus exact. Il était parfaitement possible de créer un programme VHDL qui reproduise la structure; compte tenu de la simplicité du problème, nous avons considéré que l'approche analytique était plus lisible.

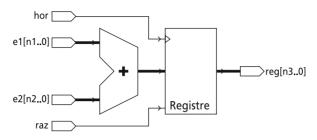

La vision hiérarchique du même additionneur consiste à traiter les blocs, l'additionneur et le registre, comme assemblage d'objets plus élémentaires. La figure A.3 en donne une image.

Figure A.3 Vision hiérarchique de l'additionneur.

La construction hiérarchique n'est, bien sûr, pas propre à VHDL. Tous les systèmes de CAO dignes de ce nom la comprennent.

Nous ne donnerons pas ici la façon de créer une hiérarchie dans le langage, chaque chose en son temps. Contentons-nous d'insister sur l'importance du concept et sur le fait que les instructions correspondantes sont extrêmement puissantes; beaucoup plus qu'il n'est possible de le figurer avec des images. VHDL inclut toute une algorithmique spatiale, qui permet de créer des structures paramétrables et évolutives.

#### Description fonctionnelle

Complémentaire de la précédente, la vision fonctionnelle apporte la puissance des langages de programmation. Au premier abord elle est assez classique, le programmeur habitué aux langages procéduraux se retrouve en terrain connu.

Le point important, qui rend VHDL très différent de langages comme C ou PASCAL, malgré les ressemblances syntaxiques fortes avec ce dernier, est que tout algorithme est la description interne d'un bloc situé quelque part dans la hiérarchie du schéma complet.

La vision structurelle est concurrente, la vision algorithmique est séquentielle, au sens informatique du terme. Un programme VHDL doit être compris comme l'assemblage, en parallèle, de tâches indépendantes qui s'exécutent concurremment. Les signaux sont, en réalité, les véhicules des informations électriques dans le schéma; vus sous l'angle quelque peu informatique précédent, ils jouent le rôle de canaux de communications interprocessus.

Avant de rentrer dans le vif du sujet, autorisons-nous un conseil : n'oubliez jamais que vous décrivez un circuit. Les langages concurrents sont parfois déconcertants pour les novices, nous avons ici la chance de traduire dans un tel langage le monde des circuits ; la vision physique des choses permet de franchir sans difficulté bien des écueils.

### PARTIE B

# CONCEPTION ET TEST DES CIRCUITS NUMÉRIQUES

VHDL est un langage de haut niveau qui permet de décrire, d'un point de vue purement fonctionnel, le comportement de systèmes numériques. Il permet également de synthétiser des circuits numériques, c'est-à-dire de traduire en schéma logique la description de ces mêmes systèmes. Certaines constructions du langage sont synthétisables et sont a fortiori simulables. D'autres sont de purs outils de modélisation, utilisables pour simuler le fonctionnement d'un système mais pas pour en faire une synthèse. C'est ici la source d'erreurs principale du débutant qui, se laissant bercer par des constructions algorithmiques parfaitement simulables, ne voit pas qu'elles ne correspondent à aucun circuit réalisable. Bien que cette frontière entre ce qui est synthétisable et ce qui ne l'est pas soit floue et se déplace à mesure que les performances d'analyse des outils de synthèse s'améliorent, la description des circuits numériques obéit à des schémas d'écriture récurrents. Ce sont quelques unes de ces structures de code synthétisables que le lecteur est invité à explorer à travers cette deuxième partie.

Dans le premier chapitre, nous explorerons les principales constructions synthétisables du langage à travers la réalisation concrète de modules classiques : décodeurs, multiplexeurs, registres, compteurs, automates, etc. Puis nous aborderons les problèmes du test unitaire et de la simulation post-synthèse. Enfin, un chapitre sera entièrement consacré aux pièges classiques qu'est susceptible de rencontrer tout concepteur débutant de circuits numériques.

## Chapitre 1

## Décrire le circuit

La description de circuits numériques en VHDL s'oriente classiquement selon trois axes complémentaires. Le premier, « comportemental » (behavioral), décrit un algorithme séquentiel, c'est-à-dire un enchaînement d'actions effectuées sur les signaux de sortie conséquemment à des observations faites sur les signaux d'entrées. La nature séquentielle de l'algorithme n'a pas de rapport avec la nature séquentielle ou combinatoire du composant décrit. Le second, « flot de données » (data flow), décrit le même algorithme par des relations causales entre signaux d'entrée et de sortie. Enfin le troisième, « structurel » (structural), correspond à l'élaboration d'un schéma où les signaux d'entrées/sorties de modules indépendants s'interconnectent pour former une architecture.

On favorisera ce dernier axe lorsqu'il s'agira de décrire un circuit complexe; on préféra les deux premiers pour les petits sous-ensembles de ce même circuit.

Après un premier aperçu de ces trois approches, nous partirons de l'algorithme (« flot de données » et « comportemental ») pour aller vers le schéma (« structurel »). Nous verrons d'abord comment décrire des opérateurs combinatoires. Puis nous traiterons des opérateurs séquentiels et des automates. Ensuite nous aborderons la description structurelle.

## 1.1 LA BOÎTE NOIRE ET SON CONTENU

Un opérateur élémentaire, un circuit intégré, une carte électronique ou un système complet sont intégralement définis par des signaux d'entrées et de sorties et par la

14 1 • Décrire le circuit

fonction qu'ils réalisent de façon interne. Ce double aspect – signaux de communication et fonction – se retrouve à tous les niveaux de la hiérarchie d'un projet. L'élément essentiel de toute description en VHDL, nommé *design entity* dans le langage, est formé par le couple *ENTITY ARCHITECTURE*. Le premier élément de ce couple décrit l'apparence externe d'une unité de conception, le second décrit son fonctionnement interne.

#### 1.1.1 La boîte noire : une entité

La déclaration d'entité décrit l'interface entre le monde extérieur et une unité de conception, c'est-à-dire principalement ses signaux d'entrées et de sorties <sup>1</sup>. Une même entité peut être associée à plusieurs architectures différentes. Elle décrit alors une classe d'unités de conception qui présentent au monde extérieur le même aspect, avec des fonctionnements internes éventuellement différents. Le même circuit peut, par exemple, être décrit de façon purement fonctionnelle lors de la conception, et de façon structurelle lors de la synthèse pour contrôler le bon respect des règles temporelles de ses constituants physiques.

#### a) Déclaration d'entité

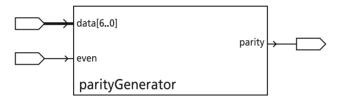

La déclaration d'entité d'un générateur de parité 7 bits s'écrit comme suit<sup>2</sup>:

```

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY parityGenerator IS

PORT (data : IN STD_LOGIC_VECTOR(6 DOWNTO 0);

even : IN STD_LOGIC;

parity : OUT STD_LOGIC);

END ENTITY parityGenerator;

```

Le signal *data* constitue les données d'entrée. L'état du signal de sortie *parity* dépendra de la polarité choisie par l'intermédiaire du signal *even*.

#### Spécification de contexte

Les deux premières lignes constituent une spécification de contexte. Elles indiquent que, dans ce module, il est fait usage de la bibliothèque *IEEE*, dont le contenu est traité en détail au chapitre 5 page 135. Ces deux lignes seront systématiquement présentes devant toutes les déclarations d'entités.

La déclaration d'entité décrit aussi les éventuels paramètres génériques de l'unité de conception (voir pages 57 et 178).

<sup>2.</sup> Les mots du langage peuvent être écrits indifféremment en majuscules ou en minuscules. Nous avons choisi les majuscules, malgré leur aspect inesthétique, pour les distinguer visuellement des mots définis par l'auteur d'une description.

#### Déclaration d'entité et spécification d'interface

Ensuite se trouve la déclaration d'entité proprement dite. Le nom de l'unité de conception figure dans l'en-tête de la déclaration (parityGenerator) et se trouve éventuellement répété à la fin.

Dans le corps de la déclaration, figure la description de l'interface de l'unité de conception : sa déclaration de port d'accès. Cette déclaration de port nous apprend que even est un signal d'entrée et que *parity* est un signal de sortie. Tout deux sont de type *STD\_LOGIC*, qui est le type standard le plus courant pour désigner une information logique <sup>1</sup>. Le signal *data* –de type *STD\_LOGIC\_VECTOR*— est également déclaré en entrée, mais représente un vecteur de sept signaux logiques numérotés de 6 à 0, dans cet ordre, autrement dit un bus.

Nous pouvons d'ores et déjà dessiner la boite noire de notre première unité de conception.

Figure 1.1 La boîte noire du générateur de parité.

#### b) Déclaration de port et modes d'accès

La déclaration de port d'accès énumère l'ensemble des signaux d'interface – les ports – qui permettent la communication entre le monde extérieur et l'unité de conception décrite. À chaque signal de communication sont attachés un nom, un mode d'accès et un type.

Un tampon bidirectionnel d'interfaçage avec un bus externe illustre parfaitement la variété des modes d'accès classiquement employés.

```

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY biDirBuffer IS

PORT (outEn : IN STD_LOGIC;

datIn : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

datOut : OUT STD_LOGIC_VECTOR (7 DOWNTO 0);

datIO : INOUT STD_LOGIC_VECTOR (7 DOWNTO 0));

END ENTITY biDirBuffer;

```

Dunod – La photocopie non autorisée est un délit

<sup>1.</sup> Nous verrons (section C.5.2 page 138) que le type *STD\_LOGIC* modélise bien plus qu'une simple information logique. En toute rigueur, c'est le type *STD\_ULOGIC* qui devrait être employé ici, mais l'usage fait que ce n'est pas le cas.